#### **Introduction to Digital Logic**

Prof. Nizamettin AYDIN

#### naydin@yildiz.edu.tr naydin@ieee.org

#### **Course Outline**

- 1. Digital Computers, Number Systems, Arithmetic Operations, Decimal, Alphanumeric, and Gray Codes

- 2. 3.

- 4.

- 5.

- Alphanumeric, and Gray Codes Binary Logic, Gates, Boolean Algebra, Standard Forms Circuit Optimization, Two-Level Optimization, Map Manipulation, Multi-Level Circuit Optimization, Two-Level Optimization, Map Manipulation, Multi-Level Circuit Optimization Additional Gates and Circuits, Other Gate Types, Exclusive-OR Operator and Gates, High-Impedance Outputs Implementation Technology and Logic Design, Design Concepts and Automation, The Design Space, Design Procedure, The major design steps Programmable Implementation Technologies: Read-Only Memories, Programmable Logic Arrays, Programmable Array Logic, Technology mapping to programmable logic devices Combinational Functions and Circuits 6.

- 7.

- 9

- Arithmetic Functions and Circuits Sequential Circuits Storage Elements and Sequential Circuit Analysis Sequential Circuits, Sequential Circuit Design State Diagrams, State Tables 10.

- 11. 12. 13. Counters, register cells, buses, & serial operations Sequencing and Control, Datapath and Control, Algorithmic State Machines (ASM) Memory Basics

# **Introduction to Digital Logic**

Lecture 8

## **Arithmetic Functions and Circuits**

#### **Overview**

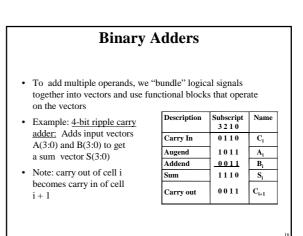

- · Iterative combinational circuits

- · Binary adders

- Half and full adders - Ripple carry and carry lookahead adders

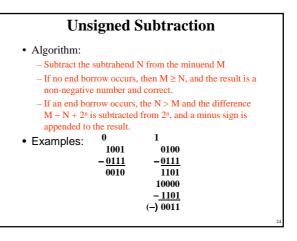

- · Binary subtraction

- · Binary adder-subtractors - Signed binary numbers

- Signed binary addition and subtraction - Overflow

- · Binary multiplication

- · Other arithmetic functions - Design by contraction

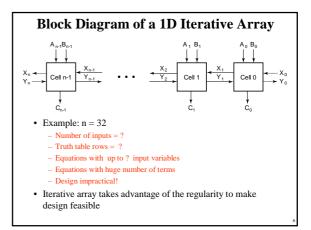

#### **Iterative Combinational Circuits**

· Arithmetic functions - Operate on binary vectors - Use the same subfunction in each bit position

- · Can design functional block for subfunction and repeat to obtain functional block for overall function

- Cell subfunction block

- Iterative array an array of interconnected cells

- An iterative array can be in a single dimension (1D) or multiple dimensions

- Binary addition used frequently

- Addition Development:

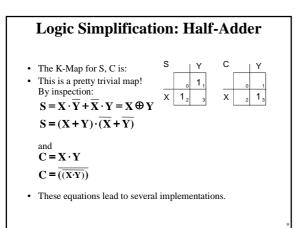

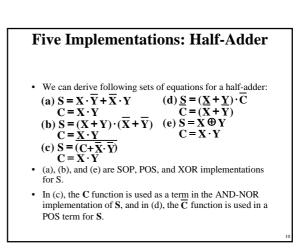

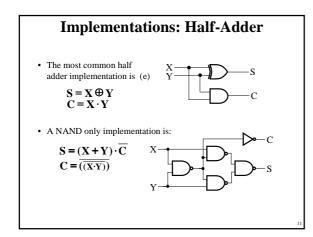

- *Half-Adder* (HA), a 2-input bit-wise addition functional block,

- *Full-Adder* (FA), a 3-input bit-wise addition functional block,

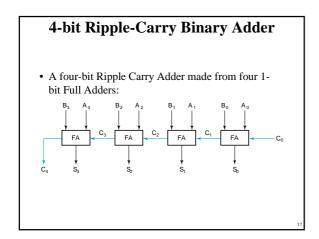

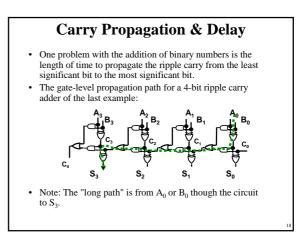

- *Ripple Carry Adder*, an iterative array to perform <u>binary addition</u>, and

- *Carry-Look-Ahead Adder* (CLA), a hierarchical structure to improve performance.

#### **Functional Block: Half-Adder** • A 2-input, 1-bit width binary adder that performs the following computations: 0 0 1 1 $\frac{+0}{00}$ $\frac{+1}{01}$ + 0 + Y +1 C S 01 10 · A half adder adds two bits to produce a two-bit sum • The sum is expressed as a X Y C S sum bit , S and a carry bit, C 0 0 0 0 The half adder can be specified 0 1 0 1 as a truth table for S and C $\Rightarrow$ 1 0 0 1 1 1 1 0

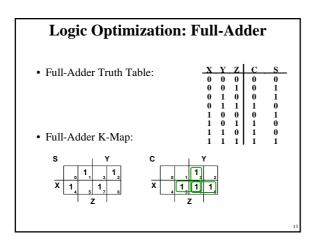

| Functional Block: Full-Adder                                                                |           |     |     |     |     |  |  |  |  |

|---------------------------------------------------------------------------------------------|-----------|-----|-----|-----|-----|--|--|--|--|

| • A full adder is similar to a h in bit from lower stages. Li a sum bit, S and a carry bit, | ke the ha |     |     |     |     |  |  |  |  |

| – For a carry-in (Z) of                                                                     | Z         | 0   | 0   | 0   | 0   |  |  |  |  |

| 0, it is the same as                                                                        | Х         | 0   | 0   | 1   | 1   |  |  |  |  |

| the half-adder:                                                                             | + Y       | + 0 | + 1 | + 0 | + 1 |  |  |  |  |

|                                                                                             | C S       | 00  | 01  | 01  | 10  |  |  |  |  |

| – For a carry- in                                                                           | _         |     |     |     |     |  |  |  |  |

| (Z) of 1:                                                                                   | Z         | 1   | 1   | 1   | 1   |  |  |  |  |

|                                                                                             | Х         | 0   | 0   | 1   | 1   |  |  |  |  |

|                                                                                             | + Y       | + 0 | + 1 | + 0 | + 1 |  |  |  |  |

|                                                                                             | C S       | 01  | 10  | 10  | 11  |  |  |  |  |

|                                                                                             |           |     |     |     | 1   |  |  |  |  |

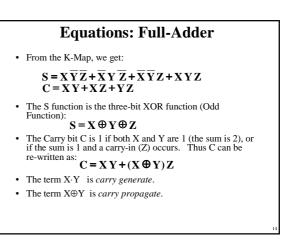

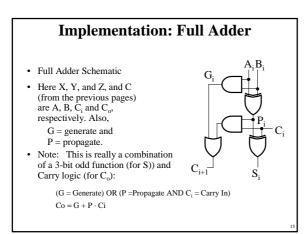

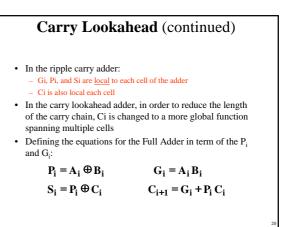

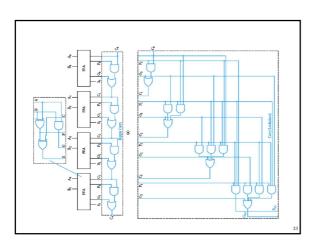

#### **Carry Lookahead**

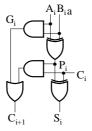

- Given Stage i from a Full Adder, we know that there will be a <u>carry generated</u> when A<sub>i</sub> = B<sub>i</sub> = "1", whether or not there is a carry-in.

- Alternately, there will be <u>carry propagated</u> if the "half-sum" is "1" and a carry-in,  $C_i$  occurs.

- These two signal conditions are called *generate*, denoted as G<sub>i</sub>, and *propagate*, denoted as P<sub>i</sub> respectively and are identified in the circuit:

#### **Carry Lookahead Development** • $C_{i+1}$ can be removed from the cells and used to derive a set of carry equations spanning multiple cells. • Beginning at the cell 0 with carry in $C_0$ : $C_1 = G_0 + P_0 C_0$ $C_2 = G_1 + P_1 C_1 = G_1 + P_1(G_0 + P_0 C_0)$ $= G_1 + P_1G_0 + P_1P_0 C_0$ $C_3 = G_2 + P_2 C_2 = G_2 + P_2(G_1 + P_1G_0 + P_1P_0 C_0)$ $= G_2 + P_2G_1 + P_2P_1G_0 + P_2P_1P_0 C_0$ $C_4 = G_3 + P_3 C_3 = G_3 + P_3G_2 + P_3P_2G_1$

$+ P_3P_2P_1G_0 + P_3P_2P_1P_0C_0$

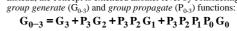

$$\mathbf{P}_{0-3} = \mathbf{P}_3 \mathbf{P}_2 \mathbf{P}_1 \mathbf{P}_0$$

• Using these two equations:

$C_4 = G_{0-3} + P_{0-3} C_0$

Thus, it is possible to have four 4-bit adders use one of the same carry lookahead circuit to speed up 16-bit addition

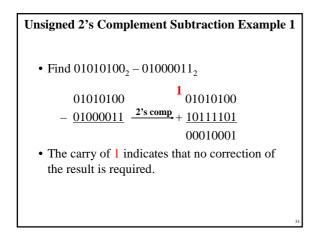

# **Binary 1's Complement** • For r = 2, $N = 01110011_2$ , n = 8 (8 digits): $(r^n - 1) = 256 - 1 = 255_{10}$ or $11111111_2$

• The 1's complement of 01110011<sub>2</sub> is then:

11111111

- 01110011

- 10001100

- Since the 2<sup>n</sup>−1 factor consists of all 1's and since 1 − 0 = 1 and 1 − 1 = 0, the one's complement is obtained by <u>complementing each individual bit</u> (bitwise NOT).

#### **Binary 2's Complement**

- For *r* = 2, *N* = 01110011<sub>2</sub>, *n* = 8 (8 digits), we have:

- $(r^n) = 256_{10}$  or  $10000000_2$

- The 2's complement of 01110011 is then: 100000000 - 01110011

- 10001101

- Note the result is the 1's complement plus 1, a fact that can be used in designing hardware

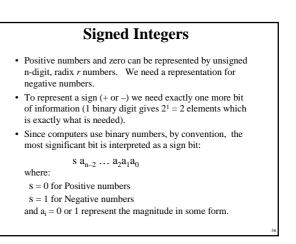

#### **Signed Integer Representations**

Signed-Magnitude – here the n – 1 digits are interpreted as a positive magnitude.

Signed-Complement – here the digits are interpreted as the rest of the complement of the number. There are two possibilities here:

- Signed 1's Complement

- Uses 1's Complement Arithmetic

Signed 2's Complement

- Uses 2's Complement Arithmetic

#### Signed Integer Representation Example

#### • r =2, n=3

| Number | Sign - Mag. | 1's Comp. | 2's Comp. |

|--------|-------------|-----------|-----------|

| +3     | 011         | 011       | 011       |

| +2     | 010         | 010       | 010       |

| +1     | 001         | 001       | 001       |

| +0     | 000         | 000       | 000       |

| -0     | 100         | 111       | _         |

| -1     | 101         | 110       | 111       |

| -2     | 110         | 101       | 110       |

| -3     | 111         | 100       | 101       |

| -4     | _           | _         | 100       |

### Signed-Magnitude Arithmetic

• If the parity of the three signs is 0:

- 1. Add the magnitudes.

- 2. Check for overflow (a carry out of the MSB)

- 3. The sign of the result is the same as the sign of the first operand.

- If the parity of the three signs is 1:

- Subtract the second magnitude from the first.

If a borrow occurs:

- take the two's complement of result

- and make the result sign the complement of the

- sign of the first operand.

- 3. Overflow will never occur.

#### **Sign-Magnitude Arithmetic Examples**

Example 1: 0 0 1 0 (+2) +0 1 0 1 (+5) 0 1 1 1 (7) 1(borrow)

Example 2: 0 0 1 0 (+2) +1 1 0 1 +(-5) 1 1 0 1 => 2s comp => 1 0 1 1 (-3) Example 3: 1 0 1 0 (-2) -0 1 0 1 -(5) 1 1 1 1 (-7)

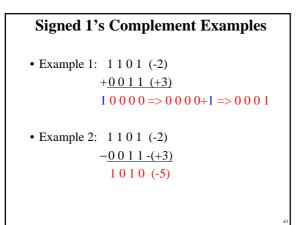

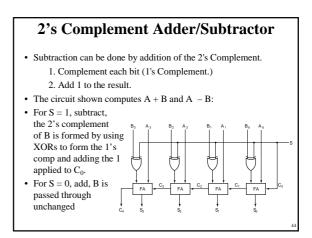

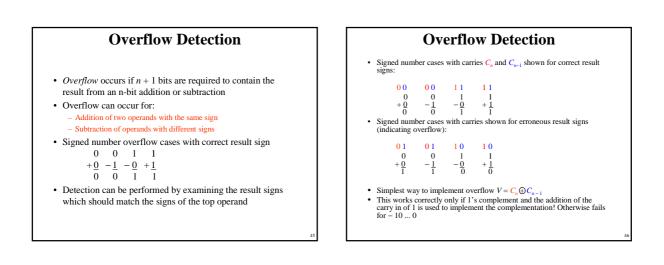

#### **Signed-Complement Arithmetic**

• Addition:

Add the numbers including the sign bits, discarding a carry out of the sign bits (2's Complement), or using an end-around carry (1's Complement).

If the sign bits were the same for both numbers and the sign of the result is different, an overflow has occurred.

The sign of the result is computed in step 1.

#### • Subtraction:

Form the complement of the number you are subtracting and follow the rules for addition.

# Signed 2's Complement Examples

- Example 1: 1 1 0 1 (-3) +0011 (+3) 10000 (0)

- Example 2: 1 1 0 1 (-3) 1 1 0 1 (-3)-0 0 1 1 -(+3) 1 1 0 1 (-3)1 0 1 0 (-6) 1 1 0 1 0 (-6)

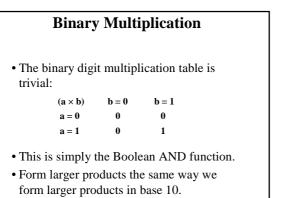

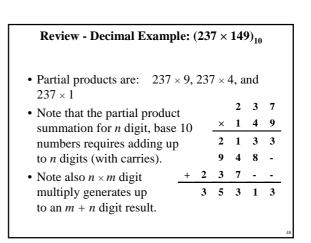

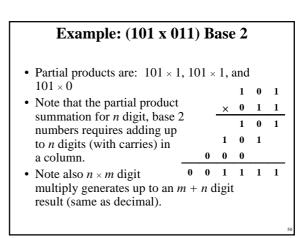

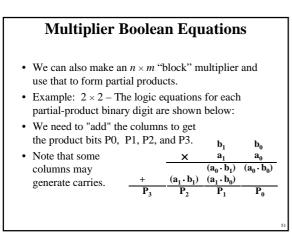

#### **Binary Multiplication Algorithm**

- We execute radix 2 multiplication by:

- Computing partial products, and

- Justifying and summing the partial products. (same as decimal)

- To compute partial products:

- Multiply the row of multiplicand digits by each multiplier digit, one at a time.

With binger unplote partial are ducts are your simple!

- With binary numbers, partial products are very simple! They are either:

all zero (if the multiplier digit is zero), or

- all zero (if the multiplier digit is zero), or

the same as the multiplicand (if the multiplier digit is one).

- Note: No carries are added in partial product formation!

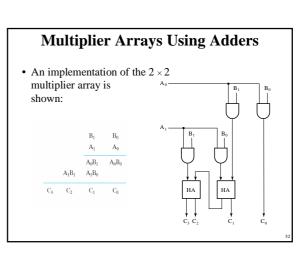

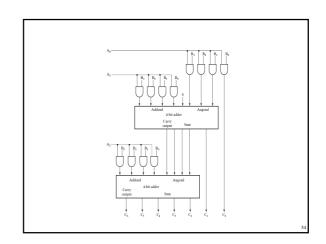

#### **Multiplier Using Wide Adders**

- A more "structured" way to develop an *n* × *m* multiplier is to sum partial products using adder trees

- The partial products are formed using an  $n \times m$  array of AND gates

- Partial products are summed using m 1 adders of width *n* bits

- Example: 4-bit by 3-bit adder

- Following figure shows a  $4 \times 3 = 12$  element array of AND gates and two 4-bit adders

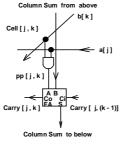

#### **Cellular Multiplier Array**

- Another way to implement multipliers is to use  $_{Cell[j,k]}$ an  $n \times m$  cellular array structure of uniform  $\swarrow$ elements as shown:

- Each element computes a single bit product equal to a<sub>i</sub>·b<sub>j</sub>, and implements a single bit full adder

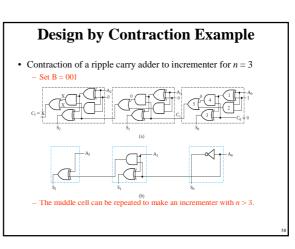

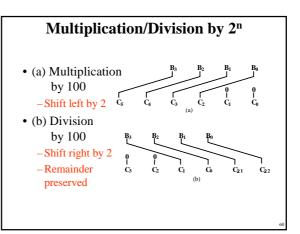

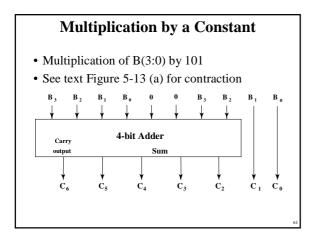

# Other Arithmetic Functions Convenient to design the functional blocks by *contraction* - removal of redundancy from circuit to which input fixing has been applied Functions Incrementing Decrementing Multiplication by Constant

- -Division by Constant

- -Zero Fill and Extension

#### **Design by Contraction**

- Contraction is a technique for simplifying the logic in a functional block to implement a different function

- The new function must be realizable from the original function by applying rudimentary functions to its inputs

- -Contraction is treated here only for application of 0s and 1s (not for X and  $\overline{X}$ )

- After application of 0s and 1s, equations or the logic diagram are simplified by using rules given on pages 224 - 225 of the text.

#### **Incrementing & Decrementing**

- Incrementing

- Adding a fixed value to an arithmetic variable

- Fixed value is often 1, called *counting (up)*

- Examples: A + 1, B + 4

- Functional block is called incrementer

- Decrementing

- Subtracting a fixed value from an arithmetic variable

- Fixed value is often 1, called *counting (down)*

- Examples: A 1, B 4

- Functional block is called decrementer

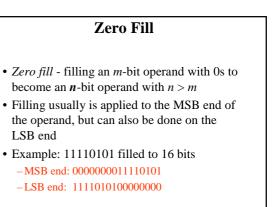

## Extension

- *Extension* increase in the number of bits at the MSB end of an operand by using a complement representation

- Copies the MSB of the operand into the new positions

- Positive operand example 01110101 extended to 16 bits: 0000000001110101

- Negative operand example 11110101 extended to 16 bits:

11111111111110101