#### **Introduction to Digital Logic**

Prof. Nizamettin AYDIN

naydin@yildiz.edu.tr naydin@ieee.org

#### **Course Outline**

- Digital Computers, Number Systems, Arithmetic Operations, Decimal, Alphanumeric, and Gray Codes

- Alphanumeric, and Gray Codes

Binary Logic, Gates, Boolean Algebra, Standard Forms

Circuit Optimization, Two-Level Optimization, Map Manipulation, Multi-Level

Circuit Optimization, Two-Level Optimization, Map Manipulation, Multi-Level

Circuit Optimization

Additional Gates and Circuits, Other Gate Types, Exclusive-OR Operator and Gates,

High-Impedance Outputs

Implementation Technology and Logic Design, Design Concepts and Automation,

The Design Space, Design Procedure, The major design steps

Programmable Implementation Technologies: Read-Only Memories, Programmable

Logic Arrays, Programmable Array Logic, Technology mapping to programmable

logic devices

Combinational Functions and Circuits

Arithmetic Functions and Circuits

- Arithmetic Functions and Circuits

Sequential Circuits Storage Elements and Sequential Circuit Analysis

Sequential Circuits, Sequential Circuit Design State Diagrams, State Tables

- Counters, register cells, buses, & serial operations Sequencing and Control, Datapath and Control, Algorithmic State Machines (ASM) Memory Basics

#### **Introduction to Digital Logic**

Lecture 7

#### **Combinational Functions and Circuits**

#### Overview

- · Functions and functional blocks

- Rudimentary logic functions

- Decoding

- Encoding

- · Selecting

- Implementing Combinational Functions Using:

- Decoders and OR gates

- Multiplexers (and inverter)

- ROMs

- PLAs

- PALs

- Lookup Tables

#### **Functions and Functional Blocks**

- The functions considered are those found to be very useful in design

- Corresponding to each of the functions is a combinational circuit implementation called a functional block.

- · In the past, many functional blocks were implemented as SSI, MSI, and LSI circuits.

- Today, they are often simply parts within a VLSI circuit.

#### **Rudimentary Logic Functions**

- Functions of a single variable X

- Can be used on the inputs to functional blocks to implement other than the block's intended function

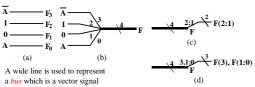

#### **Multiple-bit Rudimentary Functions**

• Multi-bit Examples:

- In (b) of the example,  $F = (F_3, F_2, F_1, F_0)$  is a bus.

- The bus can be split into individual bits as shown in (b)

- <u>Sets of bits</u> can be split from the bus as shown in (c) for bits 2 and 1 of F.

- The sets of bits need not be continuous as shown in (d) for bits 3, 1, and 0 of F.

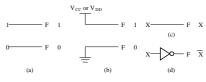

#### **Enabling Function**

- *Enabling* permits an input signal to pass through to an output

- *Disabling* blocks an input signal from passing through to an output, replacing it with a fixed value

- The value on the output when it is disable can be Hi-Z (as for three-state buffers and transmission gates), 0, or 1

• When disabled, 1 output-

Enabling applications?

Electric E

#### **Decoding**

- Decoding the conversion of an *n*-bit input code to an *m*-bit output code with n ≤ m ≤ 2<sup>n</sup> such that each valid code word produces a unique output code

- Circuits that perform decoding are called decoders

- · Here, functional blocks for decoding are

- called *n*-to-*m* line decoders, where  $m \le 2^n$ , and -generate  $2^n$  (or fewer) minterms for the *n* input

- generate  $2^n$  (or fewer) minterms for the n input variables

####

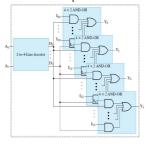

#### **Decoder Expansion**

- General procedure given in book for any decoder with n inputs and 2n outputs.

- · This procedure builds a decoder backward from the outputs.

- The output AND gates are driven by two decoders with their numbers of inputs either equal or differing by 1.

- These decoders are then designed using the same procedure until 2-to-1-line decoders are reached.

- The procedure can be modified to apply to decoders with the number of outputs  $\neq 2^n$

#### **Decoder Expansion - Example 1**

- 3-to-8-line decoder

- Number of output ANDs = 8

- Number of inputs to decoders driving output ANDs = 3

- Closest possible split to equal

- 2-to-4-line decoder

- 1-to-2-line decoder

- 2-to-4-line decoder

- Number of output ANDs = 4

- Number of inputs to decoders driving output ANDs = 2

- Closest possible split to equal

- Two 1-to-2-line decoders

##

#### **Decoder Expansion - Example 2**

- 7-to-128-line decoder

- Number of output ANDs = 128

- Number of inputs to decoders driving output ANDs = 7

- Closest possible split to equal

- 4-to-16-line decoder

- · 3-to-8-line decoder

- 4-to-16-line decoder

- Number of output ANDs = 16

- Number of inputs to decoders driving output ANDs = 2

- · Closest possible split to equal

- 2 2-to-4-line decoders

- Complete using known 3-8 and 2-to-4 line decoders

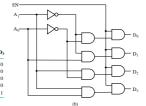

#### **Decoder with Enable**

- In general, attach *m*-enabling circuits to the outputs

- Truth table for the function

- Note use of X's to denote both 0 and 1

- Combination containing two X's represent four binary combinations

- Alternatively, can be viewed as distributing value of signal EN to

1 of 4 outputs

- In this case, called a demultiplexer

#### **Encoding**

- Encoding the opposite of decoding the conversion of an m-bit input code to a n-bit output code with n ≤ m ≤ 2<sup>n</sup> such that each valid code word produces a unique output code

- · Circuits that perform encoding are called encoders

- An encoder has  $2^n$  (or fewer) input lines and n output lines which generate the binary code corresponding to the input values

- Typically, an encoder converts a code containing exactly one bit that is 1 to a binary code corresponding to the position in which the 1 appears.

#### **Encoder Example**

- · A decimal-to-BCD encoder

- -Inputs: 10 bits corresponding to decimal digits 0 through 9,  $(D_0, ..., D_9)$

- -Outputs: 4 bits with BCD codes

- -Function: If input bit  $D_i$  is a 1, then the output  $(A_3, A_2, A_1, A_0)$  is the BCD code for i,

- The truth table could be formed, but alternatively, the equations for each of the four outputs can be obtained directly.

#### **Encoder Example (continued)**

- Input D<sub>i</sub> is a term in equation A<sub>j</sub> if bit A<sub>j</sub> is 1 in the binary value for i.

- Equations:

$$A_3 = D_8 + D_9$$

$$A_2 = D_4 + D_5 + D_6 + D_7$$

$$A_1 = D_2 + D_3 + D_6 + D_7$$

$$A_0 = D_1 + D_3 + D_5 + D_7 + D_9$$

•  $F_1 = D_6 + D_7$  can be extracted from  $A_2$  and  $A_1$

#### **Priority Encoder**

- If more than one input value is 1, then the encoder just designed does not work.

- One encoder that can accept all possible combinations of input values and produce a meaningful result is a *priority encoder*.

- Among the 1s that appear, it selects the most significant input position (or the least significant input position) containing a 1 and responds with the corresponding binary code for that position.

#### **Priority Encoder Example**

Priority encoder with 5 inputs (D<sub>4</sub>, D<sub>3</sub>, D<sub>2</sub>, D<sub>1</sub>, D<sub>0</sub>) - highest priority to most significant 1 present - Code outputs A2, A1, A0 and V where V indicates at least one 1 present.

| No. of Min- | Inputs |    |    |    | Outputs |    |    |    |   |

|-------------|--------|----|----|----|---------|----|----|----|---|

| terms/Row   | D4     | D3 | D2 | D1 | D0      | A2 | A1 | A0 | V |

| 0           | 0      | 0  | 0  | 0  | 0       | X  | X  | X  | 0 |

| 1           | 0      | 0  | 0  | 0  | 1       | 0  | 0  | 0  | 1 |

| 2           | 0      | 0  | 0  | 1  | X       | 0  | 0  | 1  | 1 |

| 4           | 0      | 0  | 1  | X  | X       | 0  | 1  | 0  | 1 |

| 8           | 0      | 1  | X  | X  | X       | 0  | 1  | 1  | 1 |

| 16          | 1      | X  | X  | X  | X       | 1  | 0  | 0  | 1 |

Xs in input part of table represent 0 or 1; thus table entries correspond to

product terms instead of minterms. The column on the left shows that all 32

minterms are present in the product terms in the table

#### **Priority Encoder Example** (continued)

Could use a K-map to get equations, but can be read directly from table and manually optimized if careful:

$$\begin{split} & A_2 = D_4 \\ & A_1 = \overline{D}_4 D_3 + \overline{D}_4 \overline{D}_3 D_2 = \overline{D}_4 F_1, \ F_1 = (D_3 + D_2) \\ & A_0 = \overline{D}_4 D_3 + \overline{D}_4 \overline{D}_3 \overline{D}_2 D_1 = \overline{D}_4 (D_3 + \overline{D}_2 D_1) \\ & V = D_4 + F_1 + D_1 + D_0 \end{split}$$

#### **Selecting**

- Selecting of data or information is a critical function in digital systems and computers

- Circuits that perform selecting have:

- -A set of information inputs from which the selection is made

- -A single output

- -A set of control lines for making the selection

- Logic circuits that perform selecting are called *multiplexers*

- Selecting can also be done by three-state logic or transmission gates

#### Multiplexers

- A multiplexer selects information from an input line and directs the information to an output line

- A typical multiplexer has n control inputs (S<sub>n-1</sub>, ... S<sub>0</sub>) called *selection inputs*, 2<sup>n</sup> information inputs (I<sub>2</sub><sup>n</sup><sub>-1</sub>, ... I<sub>0</sub>), and one output Y

- A multiplexer can be designed to have *m* information inputs with m < 2<sup>n</sup> as well as *n* selection inputs

#### 2-to-1-Line Multiplexer

- Since  $2 = 2^1$ , n = 1

- The single selection variable S has two values:

- -S = 0 selects input  $I_0$

- -S = 1 selects input  $I_1$

- The equation:

$$\mathbf{Y} = \overline{\mathbf{S}}\mathbf{I_0} + \mathbf{S}\mathbf{I_1}$$

• The circuit:

Decoder Enabling Circuits

#### 2-to-1-Line Multiplexer (continued)

- Note the regions of the multiplexer circuit shown:

- 1-to-2-line Decoder

- 2 Enabling circuits

- 2-input OR gate

- To obtain a basis for multiplexer expansion, we combine the Enabling circuits and OR gate into a 2 × 2 AND-OR circuit:

- 1-to-2-line decoder

- $-2 \times 2$  AND-OR

- In general, for an  $2^n$ -to-1-line multiplexer:

- -n-to- $2^n$ -line decoder

- $-2^n \times 2$  AND-OR

###

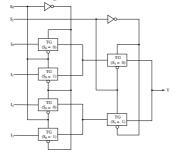

#### **Multiplexer Width Expansion**

- · Select "vectors of bits" instead of "bits"

- Use multiple copies of  $2^n \times 2$  AND-OR in parallel

- Example: 4-to-1-line quad multiplexer

#### **Other Selection Implementations**

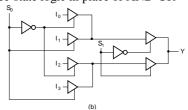

• Three-state logic in place of AND-OR

• Gate input cost = 14 compared to 22 (or 18) for gate implementation

#### **Other Selection Implementations**

- Transmission Gate Multiplexer

- Gate input cost = 8 compared to 14 for 3-state logic and 18 or 22 for gate logic

#### **Combinational Function Implementation**

- · Alternative implementation techniques:

- Decoders and OR gates

- Multiplexers (and inverter)

- ROMs

- PLAs

- PALs

- Lookup Tables

- Can be referred to as *structured implementation methods* since a specific underlying structure is assumed in each case

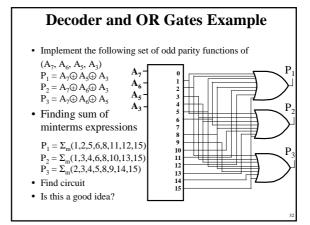

#### **Decoder and OR Gates**

- Implement *m* functions of *n* variables with:

- Sum-of-minterms expressions

- One n-to- $2^n$ -line decoder

- -m OR gates, one for each output

- Approach 1:

- Find the truth table for the functions

- Make a connection to the corresponding OR from the corresponding decoder output wherever a 1 appears in the truth table

- Approach 2

- Find the minterms for each output function

- OR the minterms together

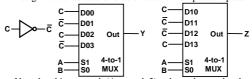

#### **Multiplexer Approach 1**

- Implement *m* functions of *n* variables with:

- Sum-of-minterms expressions

- An *m*-wide 2<sup>*n*</sup>-to-1-line multiplexer

- Design:

- Find the truth table for the functions.

- In the order they appear in the truth table:

- Apply the function input variables to the multiplexer inputs  $\boldsymbol{S}_{n-1},\,\ldots\,,\,\boldsymbol{S}_0$

- Label the outputs of the multiplexer with the output variables

- Value-fix the information inputs to the multiplexer using the values from the truth table (for don't cares, apply either 0 or 1)  $\,$

#### **Example: Gray to Binary Code**

- · Design a circuit to convert a 3-bit Gray code to a binary code

- The formulation gives the truth table on the right

- It is obvious from this table that X = C and the Y and Z are more complex

| Gray  | Binary |

|-------|--------|

| A B C | хуz    |

| 000   | 000    |

| 100   | 0 0 1  |

| 110   | 010    |

| 010   | 011    |

| 0 1 1 | 100    |

| 111   | 101    |

| 101   | 110    |

| 001   | 111    |

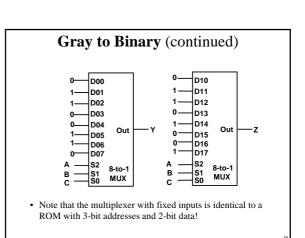

#### **Gray to Binary** (continued)

- Rearrange the table so that the input combinations are in counting order

- Functions y and z can be implemented using a dual 8-to-1-line multiplexer by:

- connecting A, B, and C to the multiplexer select inputs

- placing y and z on the two multiplexer outputs

- connecting their respective truth table values to the inputs

| Gray  | Binary |

|-------|--------|

| A B C | хух    |

| 000   | 000    |

| 0 0 1 | 111    |

| 010   | 011    |

| 0 1 1 | 100    |

| 100   | 0 0 1  |

| 101   | 110    |

| 110   | 010    |

| 111   | 1.0.1  |

#### **Multiplexer Approach 2**

- Implement any m functions of n + 1 variables by using:

- An m-wide 2<sup>n</sup>-to-1-line multiplexer

- A single inverter

- Design:

- Find the truth table for the functions.

- Based on the values of the first n variables, separate the truth table rows into pairs

- For each pair and output, define a rudimentary function of the final variable  $(0,1,X,\overline{X})$

- Using the first n variables as the index, value-fix the information inputs to the multiplexer with the corresponding rudimentary functions

- Use the inverter to generate the rudimentary function  $\overline{\boldsymbol{X}}$

#### **Example: Gray to Binary Code**

- Design a circuit to convert a 3-bit Gray code to a binary code

- The formulation gives the truth table on the right

- It is obvious from this table that x = C and the Y and Z are more complex

| Gray  | Binary |

|-------|--------|

| ABC   | хуz    |

| 000   | 000    |

| 100   | 001    |

| 110   | 010    |

| 010   | 0 1 1  |

| 0 1 1 | 100    |

| 111   | 101    |

| 101   | 110    |

| 0 0 1 | 111    |

#### Gray to Binary (continued)

Rearrange the table so that the input combinations are in counting order, pair rows, and find rudimentary functions

| Gray<br>A B C  | Binary<br>x y z | Rudimentary<br>Functions of C<br>for y | Rudimentary<br>Functions of C<br>for z |  |

|----------------|-----------------|----------------------------------------|----------------------------------------|--|

| 000            | 0 0 0           | F = C                                  | F = C                                  |  |

| 010            | 0 1 1           | $\mathbf{F} = \overline{\mathbf{C}}$   | $\mathbf{F} = \overline{\mathbf{C}}$   |  |

| 100            | 0 0 1           | F = C                                  | $\mathbf{F} = \overline{\mathbf{C}}$   |  |

| 1 1 0<br>1 1 1 | 0 1 0<br>1 0 1  | F = \overline{C}                       | F = C                                  |  |

#### **Gray to Binary (continued)**

• Assign the variables and functions to the multiplexer inputs:

- Note that this approach (Approach 2) reduces the cost by almost half compared to Approach 1.

- This result is no longer ROM-like

- Extending, a function of more than n variables is decomposed into several <u>sub-functions</u> defined on a subset of the variables. The multiplexer then selects among these sub-functions.

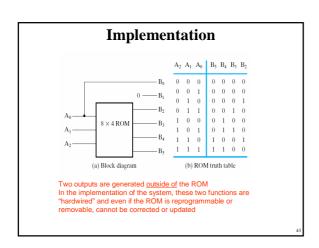

#### **Read Only Memory**

- Functions are implemented by storing the truth table

- Other representations such as equations more convenient

- Generation of programming information from equations usually done by software

- Text Example 4-10: Design a combinational circuit using a ROM. The circuit accepts a 3 bit number and generates an output binary number equal to the square of the input number

#### Truth table

| Inputs         |                | Outputs               |                |                |                |                |                |                |         |

|----------------|----------------|-----------------------|----------------|----------------|----------------|----------------|----------------|----------------|---------|

| A <sub>2</sub> | A <sub>1</sub> | <b>A</b> <sub>0</sub> | B <sub>5</sub> | B <sub>4</sub> | B <sub>3</sub> | B <sub>2</sub> | B <sub>1</sub> | B <sub>0</sub> | Decimal |

| 0              | 0              | 0                     | 0              | 0              | 0              | 0              | 0              | 0              | 0       |

| 0              | 0              | 1                     | 0              | 0              | 0              | 0              | 0              | 1              | 1       |

| 0              | 1              | 0                     | 0              | 0              | 0              | 1              | 0              | 0              | 4       |

| 0              | 1              | 1                     | 0              | 0              | 1              | 0              | 0              | 1              | 9       |

| 1              | 0              | 0                     | 0              | 1              | 0              | 0              | 0              | 0              | 16      |

| 1              | 0              | 1                     | 0              | 1              | 1              | 0              | 0              | 1              | 25      |

| 1              | 1              | 0                     | 1              | 0              | 0              | 1              | 0              | 0              | 36      |

| 1              | 1              | 1                     | 1              | 1              | 0              | 0              | 0              | 1              | 49      |

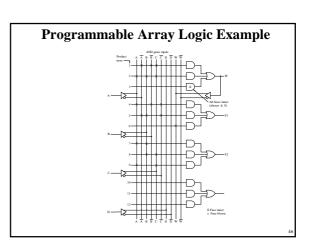

#### **Programmable Array Logic**

- There is no sharing of AND gates as in the ROM and PLA

- Design requires fitting functions within the limited number of ANDs per OR gate

- Single function optimization is the first step to fitting

- Otherwise, if the number of terms in a function is greater than the number of ANDs per OR gate, then factoring is necessary

#### **Programmable Array Logic Example**

- Equations:  $F1 = A\overline{B} \overline{C} + \overline{A} B\overline{C} + \overline{A} \overline{B} C + ABC$ F2 = AB + BC + AC

- F1 must be factored since four terms

- Factor out last two terms as W

| Product<br>term |   | Αħ | ND Inp |   |   |                                   |

|-----------------|---|----|--------|---|---|-----------------------------------|

|                 | A | В  | С      | D | w | Outputs                           |

|                 | 0 | 0  | 1      | _ | _ | $W = \overline{A} \overline{B} C$ |

| 2               | 1 | 1  | 1      | _ | _ | + ABC                             |

| 3               | _ | _  | _      | _ | _ |                                   |

| ļ               | 1 | 0  | 0      | _ | _ | F1 = X = A B C                    |

| 5               | 0 | 1  | 0      | _ | _ | + AB C+ W                         |

| 5               | _ | _  | _      | _ | 1 | + AB C+ W                         |

| ,               | 1 | 1  | _      | _ | _ | F2 = Y                            |

| 3               | _ | 1  | 1      | _ | _ |                                   |

| )               | 1 | _  | 1      | _ | _ | = AB + BC + AC                    |

| .0              | _ | _  | _      | _ | _ |                                   |

| 1               | _ | _  | _      | _ | _ |                                   |

| 12              | _ | _  | _      | _ | _ |                                   |

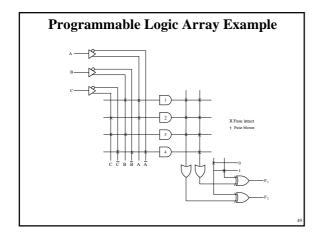

#### **Programmable Logic Array**

- The set of functions to be implemented must fit the available number of product terms

- The number of literals per term is less important in fitting

- The best approach to fitting is multiple-output, two-level optimization (which has not been discussed)

- Since output inversion is available, terms can implement either a function or its complement

- For small circuits, K-maps can be used to visualize product term sharing and use of complements

- For larger circuits, software is used to do the optimization including use of complemented functions

# Programmable Logic Array Example • K-map specification • How can this be implemented with four terms? • Complete the programming table $F_{1} = \overline{ABC} + \overline{ABC} + \overline{ABC} - F_{2} = \overline{AB} + \overline{AC} + \overline{AB} + \overline{BC} - F_{2} = \overline{AB} + \overline{AC} + \overline{AB} + \overline{BC} - \overline{AB} + \overline{AC} + +$

#### **Lookup Tables**

- Lookup tables are used for implementing logic in Field-Programmable Gate Arrays (FPGAs) and Complex Logic Devices (CPLDs)

- Lookup tables are typically small, often with four inputs, one output, and 16 entries

- Since lookup tables store truth tables, it is possible to implement any 4-input function

- Thus, the design problem is how to optimally decompose a set of given functions into a set of 4-input two-level functions.

- We will illustrate this by a manual attempt

#### **Lookup Table Example**

- Equations to be implemented:  $F_1(A,B,C,D,E) = A D E + B D E + C D E$   $F_2(A,B,D,E,F) = A D E + B D E + F D E$

- Extract 4-input function:  $F_3(A,B,D,E) = A D E + B D E$   $F_1(C,D,E,F_3) = F_3 + C D E$  $F_2(D,E,F,F_3) = F_3 + F D E$

- The cost of the solution is 3 lookup tables

Copyright 2000 N. AYDIN. All rights reserved.