### **Electronic Circuits**

Prof. Nizamettin AYDIN naydin@yildiz.edu.tr

http://www.yildiz.edu.tr/~naydin

Dr. Gökhan Bilgin gokhanb@ce.yildiz.edu.tr

### **Linear Digital ICs**

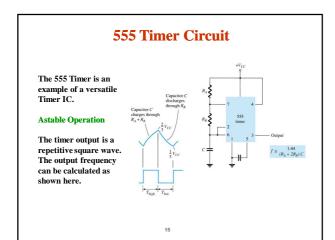

Digital/analog converters Timers Voltage-controlled oscillators Phase-locked loop circuits Interface circuits

## **Comparator Circuit**

The operation is a basic comparison. The output swings between its maximum and minimum voltage, depending upon whether one input  $(V_{in})$  is greater or less than the other  $(V_{ref})$ .

$$\label{eq:theorem} \begin{split} & The \ output \ is \ always \ a \ square \ wave \ where: \\ & \bullet \quad The \ maximum \ high \ output \ voltage \ is \ +V_{SAT}. \\ & \bullet \quad The \ minimum \ low \ output \ voltage \ is \ -V_{SAT}. \end{split}$$

### **Noninverting Op-Amp Comparator**

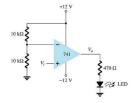

For a noninverting op-amp comparator:

- The output goes to  $+V_{SAT}$  when input  $V_i$  is greater than the reference voltage. The output goes to  $-V_{SAT}$  when

- input V<sub>i</sub> is less than the reference voltage.

- $V_{ref}$  in this circuit is +6V (taken from the voltage divider) +V  $_{SAT}$  = +V, or +12V  $-V_{SAT}$  = -V or -12V

When  $V_i$  is greater than +6V the output swings to +12V and the LED goes on. When  $V_i$  is less than +6V the output is at -12V and the LED goes off.

### **Inverting Op-Amp Comparator**

For an inverting op-amp comparator:

- The output goes to  $-V_{SAT}$  when The output goes to  $-v_{SAT}$  when input  $V_i$  is greater than the reference voltage.

The output goes to  $+V_{SAT}$  when input  $V_i$  is less than the reference voltage.

## ▼≈ LED

- $V_{ref}$  in this circuit is +6V (taken from the voltage divider) +V  $_{SAT}$  = +V, or +12V  $-V_{SAT}$  = -V or -12V

When  $V_i$  is greater than +6V the output swings to –12V and the LED goes off. When  $V_i$  is less than +6V the output is at +12V and the LED goes on.

### **Comparator ICs**

- Faster switching

- Built-in noise immunity

- · Outputs capable of directly driving loads

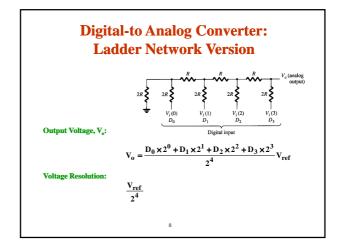

### **Digital-Analog Converters**

### Types:

- Digital-to-analog converters (ADCs)

- Analog-to-digital converters (DACs)

7

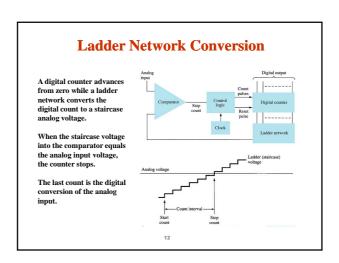

### **Analog-to-Digital Converters**

### Types:

- · Dual Slope Conversion

- Ladder Network Conversion

9

# Analog-to-Digital Conversion Dual Slope Conversion Analog input Slope Conversion The analog input voltage is applied to an integrator or ramp-generator circuit. The digital output is obtained from a digital counter that is operated during both positive and negative slope (ramp) intervals of the integrator.

### **Dual Slope Conversion**

### Rising Slope

For a fixed interval the analog voltage is applied to the integrator. The integrator output rises to some positive level. This positive voltage is applied to a comparator. At the end of the fixed interval, the counter is reset to 0. An electronic switch connects the integrator input to a fixed input or reference voltage.

### Falling Slope

The integrator output decreases at a fixed rate. The counter advances during this time. When the integrator output (connected to the comparator input) falls below the reference level of the comparator, control logic stops the counter. The digital counter output is the digital conversion of the analog input.

11

### **Resolution of Analog-to-Digital Converters**

The resolution depends on the amount of voltage per step (digital bit):

$$\frac{V_{ref}}{2^n}$$

where n is the number of digital bits

Example: A 12-bit ADC with a 10V reference level has the following resolution:

$$\frac{V_{ref}}{2^n} = \frac{10V}{2^{12}} = 2.4mV$$

13

### **Analog-to-Digital Conversion Time**

The conversion time depends on the clock frequency of the counter.

$$T_{conv} = \frac{2^n}{f}$$

where

$$\begin{split} T_{conv} &= conversion \ time \ (seconds) \\ n &= number \ of \ binary \ bits \\ f &= clock \ frequency \ for \ the \ counter \end{split}$$

Example: A 12bit ADC with a 1MHz clock has a maximum conversion time.

$$2^{12} \left( \frac{1}{1 \text{MHz}} \right) = 4.1 \text{ms}$$

14

###