## **Electronic Circuits**

Prof. Nizamettin AYDIN <u>naydin@yildiz.edu.tr</u> http://www.yildiz.edu.tr/~naydin

Dr. Gökhan Bilgin gokhanb@ce.yildiz.edu.tr

# **Digital devices**

- Introduction

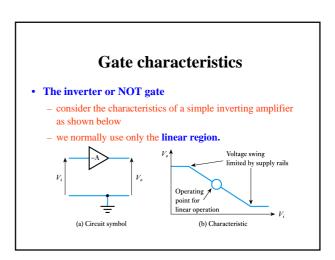

- Gate characteristics

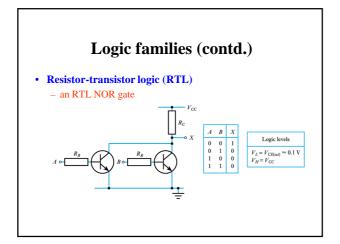

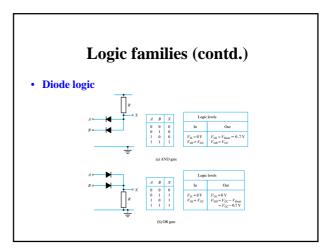

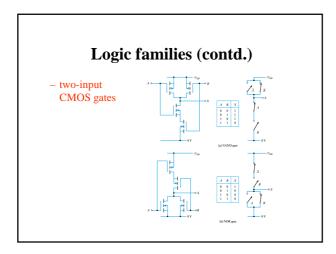

- Logic families

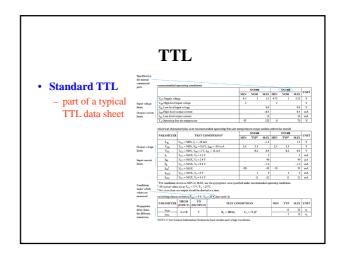

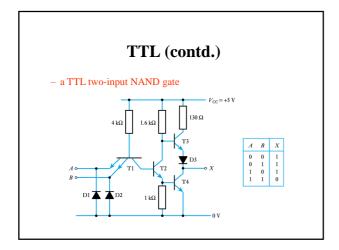

- TTL

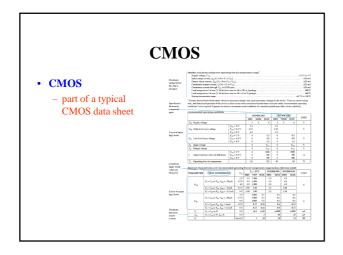

- CMOS

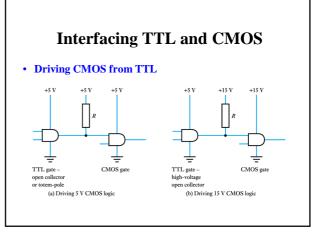

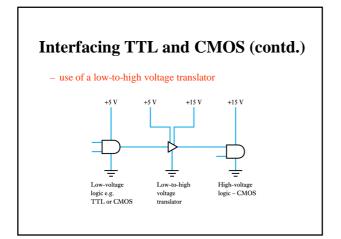

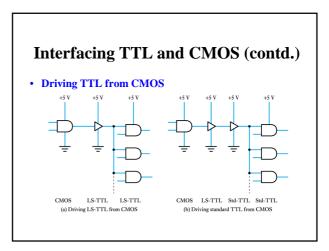

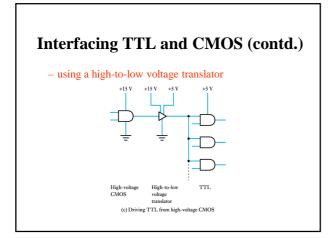

- Interfacing

- Noise and EMC in digital systems.

## Introduction

- Earlier we looked at a range of digital applications based on logic gates – at that time we treated the gates as 'black boxes'.

- We will now consider the construction of such gates, and their characteristics.

- Many terms are used to describe integration level.

- In this lecture we will concentrate on **small** and **medium**scale integration circuits containing just a handful of gates.

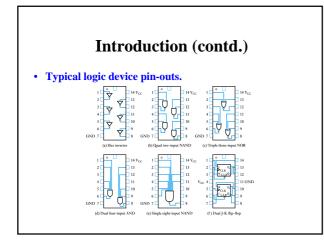

# **Introduction (contd.)**

| Integration level                    | Number of transistors               |

|--------------------------------------|-------------------------------------|

| Zero scale integration (ZSI)         | 1                                   |

| Small scale integration (SSI)        | 2–30                                |

| Medium scale integration (MSI)       | 30 - 10 <sup>3</sup>                |

| Large scale integration (LSI)        | 10 <sup>3</sup> - 10 <sup>5</sup>   |

| Very large scale integration (VLSI)  | $10^5 - 10^7$                       |

| Ultra large scale integration (ULSI) | 10 <sup>7</sup> - 10 <sup>9</sup>   |

| Giga-scale integration (GSI)         | 10 <sup>9</sup> - 10 <sup>11</sup>  |

| Tera-scale integration (TSI)         | 10 <sup>11</sup> - 10 <sup>13</sup> |

|                                      |                                     |

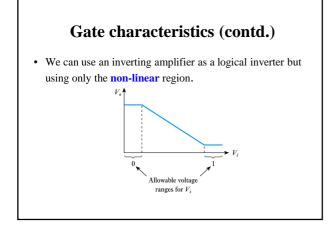

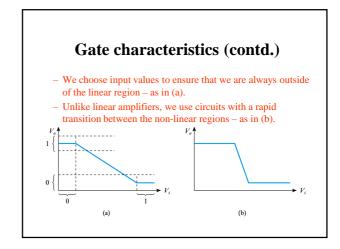

# Gate characteristics (contd.)

#### • Logic levels

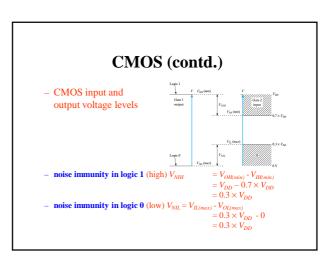

- The voltage ranges representing '0' and '1' represent the **logic levels** of the circuit.

- Often logic 0 is represented by a voltage close to 0 V but the allowable voltage range varies considerably.

- The voltage used to represent logic 1 also varies greatly. In some circuits it might be 2-4 V, while in others it might be 12-15 V.

- In order for one gate to work with another the logic levels must be compatible.

# Gate characteristics (contd.)

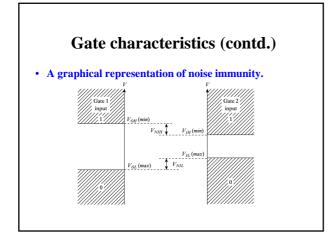

#### • Noise immunity

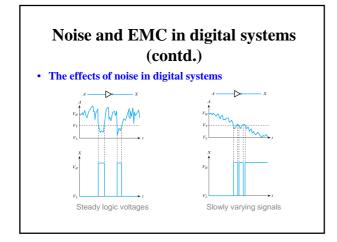

- Noise is present in all real systems.

- This adds random fluctuations to voltages representing logic levels.

- To cope with noise, the voltage ranges defining the logic levels are more tightly constrained at the output of a gate than at the input.

- Thus small amounts of noise will not affect the circuit.

- The maximum noise voltage that can be tolerated by a circuit is termed its **noise immunity**,  $V_{NI}$ .

# Gate characteristics (contd.)

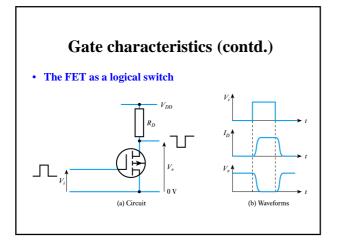

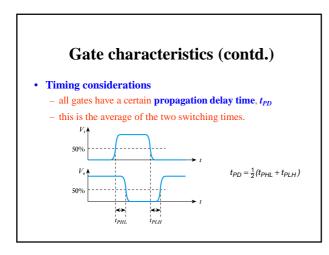

#### Transistors as switches

- Both FETs and bipolar transistors make good switches.

- Neither form produce *ideal* switches and their characteristics are slightly different.

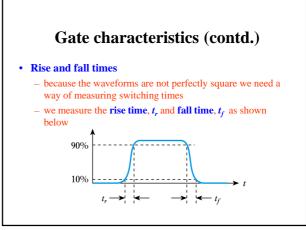

- Both forms of device take a finite time to switch and this produces a slight delay in the operation of the gate.

- This is termed the **propagation delay** of the circuit.

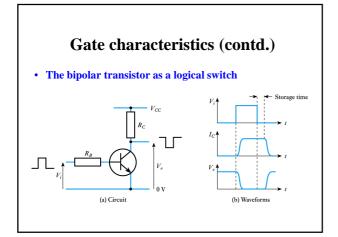

# Gate characteristics (contd.)

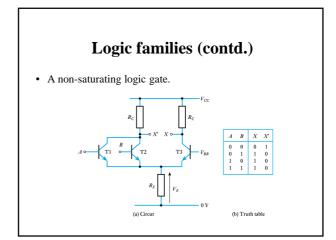

- When the input voltage to a bipolar transistor is high the transistor turns ON and the output voltage is driven down to its saturation voltage, which is about 0.1 V.

- However, saturation of the transistor results in the storage of excess charge in the base region.

- This increases the time taken to turn OFF the device an effect known as **storage time.**

- This makes the device faster to turn ON than OFF.

- Some switching circuits increase speed by preventing the transistors from entering saturation.

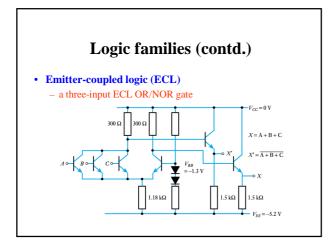

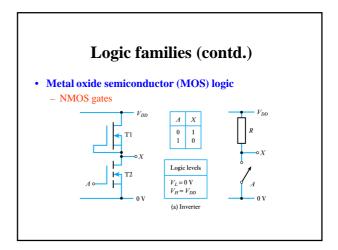

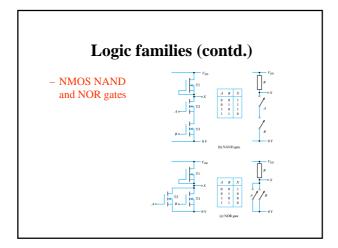

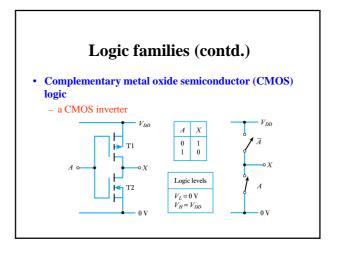

| A compa              | arison o  | of logic f | amilies   |

|----------------------|-----------|------------|-----------|

| Parameter            | TTL       | ECL        | CMOS      |

| Basic gate           | NAND      | OR/NOR     | NAND-NOR  |

| Fan-out              | 10        | 25         | >50       |

| Power per gate (mW)  | 1 – 22    | 4 - 55     | 1@1 MHz   |

| Noise immunity       | Very good | Good       | Excellent |

| T <sub>PD</sub> (ns) | 1.5 – 33  | 1 – 4      | 1.5 – 200 |

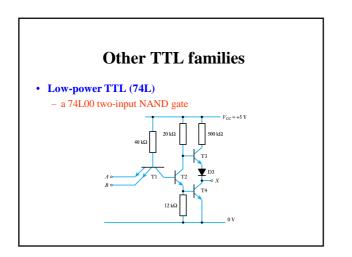

A comparison of TTL families

| Family                      | Descriptor | <i>T<sub>PD</sub></i> (ns) | Power per<br>gate (mW) |

|-----------------------------|------------|----------------------------|------------------------|

| Standard                    | 74XX       | 9                          | 10                     |

| Low-power                   | 74LXX      | 33                         | 1                      |

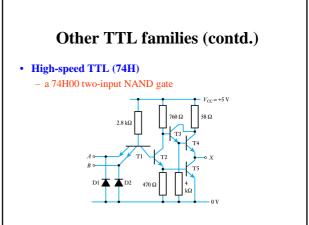

| High-speed                  | 74HXX      | 6                          | 22                     |

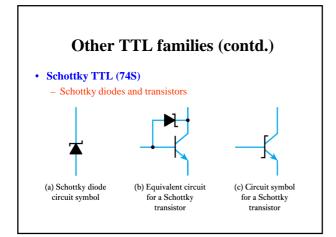

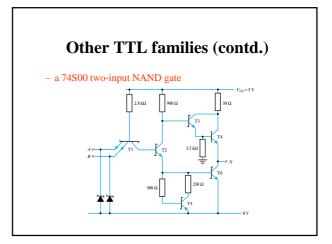

| Schottky                    | 74SXX      | 3                          | 19                     |

| Advanced Schottky           | 74ASXX     | 1.5                        | 8.5                    |

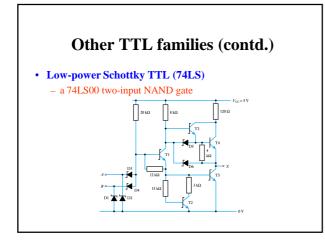

| Low-power Schottky          | 74LSXX     | 9.5                        | 2                      |

| Advanced low-power Schottky | 74ALSXX    | 4                          | 1                      |

| FAST                        | 74FXX      | 2.7                        | 4                      |

# CMOS (contd.)

#### • CMOS inputs

- CMOS gate protection circuitry

- CMOS inputs must not be left unconnected

- unused inputs should be tied to ground (logic 0) or to the positive supply rail (logic 1)

- unused inputs to an AND or NAND gate should be tied high

- unused inputs to an OR or NOR gate should be tied *low*.

### CMOS (contd.)

#### • CMOS outputs

- typical output resistance of about  $250\Omega$  (5V operation)

- high input resistance produces a high fan-out

- propagation delay increases with the number of gates being driven

- if high-speed operation is not required, at least 50 gates can be driven from a single output

- no CMOS equivalent of open-collector output

- some CMOS gates have three-state facility.

## **CMOS** families

#### • Standard CMOS (4000B)

- one of the oldest form of CMOS now largely obsolete

- operates with supply voltages of 3-18 V

- can produce very high noise immunity (typically about 0.45  $\times V_{CC}$ )

- relatively slow propagation delay times of 45-125 ns.

## CMOS families (contd.)

#### • Standard CMOS with TTL pin-out (74C)

- adopts a device numbering scheme compatible with corresponding TTL parts

- operates with supply voltages of 3–18 V

- can produce very high noise immunity (typically about 0.45  $\times V_{CC}$ )

- relatively slow propagation delay times of 30-50 ns.

## CMOS families (contd.)

#### • High-speed CMOS (74HC)

- will operate with supply voltages of 2–6 V, but often uses a 5 V supply

- significantly faster than standard CMOS ( $T_{PD} \approx 8$ ns)

- High-speed CMOS, TTL compatible inputs (74HCT)

- another high-speed family, which offers TTL compatible inputs

- operates with supply voltages of 4.5-5.5 V

- direct replacements for similar TTL parts, with similar speeds to 74LS parts.

## **CMOS families (contd.)**

#### Advanced CMOS (74AC)

- offer a significant speed advantage over high-speed CMOS (*T<sub>PD</sub>* ≈ 4ns), with similar power consumption

will operate with supply voltages of 2–6 V

- will operate with suppry voltages of 2-0 v

- Advanced CMOS, TTL compatible inputs (74ACT)

offers similar performance to Advanced CMOS, but has

TTL compatible inputs

- operates with supply voltages of 4.5-5.5 V.

# CMOS families (contd.)

- Low-voltage CMOS (74LV)

- can be used with supply voltages of 2 5.5 V, permitting low voltage operation where necessary

- Advanced, low-voltage CMOS (74ALVC)

- this advanced low-voltage family can be used with supply voltages between 1.65 and 3.6 V

- provides considerable speed advantage compared to the 74LV series

- $T_{PD}$  might be 3 ns when used with a supply voltage of 3.0 V, increasing to 4.4 ns when used at 1.8 V.

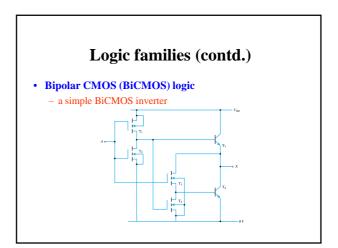

# **CMOS families (contd.)**

- BiCMOS (74BCT)

- provides a range of high-speed input/output and device driver circuits

- normally used with a supply voltage of 5 V, but will accept supply voltages in the range  $4.5-5.5~\rm V$

- typical  $T_{PD}$  about 3–4 ns.

- Low-voltage BiCMOS (74LVT)

- offers BiCMOS operation in a family that can be used with supply voltages between 2.7 and 3.6 V.

## A comparison of CMOS families

| Family                     | Descriptor | T <sub>PD</sub> (ns) | Static power<br>per gate (µW) |

|----------------------------|------------|----------------------|-------------------------------|

| Standard                   | 4000B      | 75                   | 50                            |

| Standard, TTL pin-out      | 74CXX      | 50                   | 50                            |

| High-speed                 | 74HCXX     | 8                    | 25                            |

| High-speed, TTL compatible | 74HCTXX    | 12                   | 25                            |

| Advanced                   | 74ACXX     | 4                    | 25                            |

| Advanced, TTL compatible   | 74ACTXX    | 6                    | 25                            |

| Low-voltage                | 74LVXX     | 9                    | 50                            |

| Advanced, low-voltage      | 74ALVCXX   | 3                    | 50                            |

| BiCMOS                     | 74BCTXX    | 3.5                  | 600                           |

| Low-voltage BiCMOS         | 74LVTXX    | 4                    | 400                           |

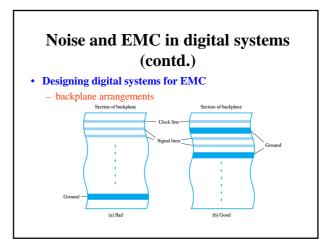

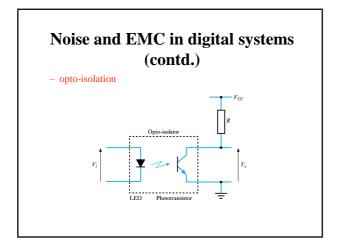

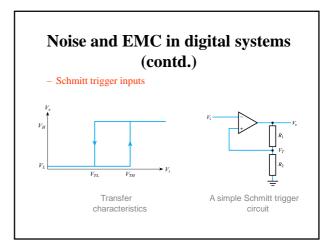

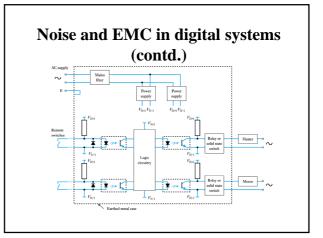

# Noise and EMC in digital systems (contd.)

# A design example

#### An industrial control system

A system is connected to **two remote mechanical switches**, and to an **AC heater** and an **AC motor**. The controller is required to take signals from the switches and to turn the heater and motor ON and OFF according to some control algorithm. The system is to be used in an environment with a **high level of electrical noise**. Suggest how the unit could be designed to minimize the effects of noise on its operation.

## **Key points**

- Physical gates are not ideal components.

- Logic gates are manufactured in a range of logic families.

- The ability of a gate to ignore noise is its 'noise immunity'.

- Both MOSFETs and bipolar transistors are used in gates.

- All logic gates exhibit a propagation delay.

- · The most widely used logic families are TTL and CMOS.

- Both TTL and CMOS gates are produced in a range of versions, each optimised for a particular characteristic.

- Interface circuitry may be needed to link devices of different families.

- Noise and EMC issues must be considered during design.