Copyright 2000 N. AYDIN. All rights reserved.

#### Source and Result Operands

- Source and Result Operands can be in one of the following areas:

- Main memory

- Virtual memory

- Cache

- CPU register

- I/O device

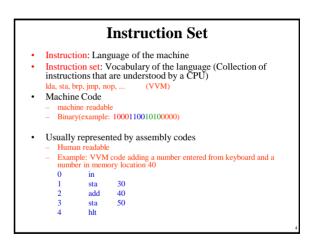

#### **Instruction Representation**

- In machine code each instruction has a unique bit pattern

- For human consumption a symbolic representation is used (assembly language)

- Opcodes are represented by abbreviations, called mnemonics indicating the operation

- ADD, SUB, LDA, BRP, ...

• In an assembly language, operands can also be represented as following

```

- ADD A,B (add contents of B and A and save the result into A)

```

| Zei                              | ro Address Machine                                                                                                                              |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| • a.k.a. Stack                   | Machines                                                                                                                                        |

| • Example:                       | a = b + c;                                                                                                                                      |

| PUSH b<br>PUSH c<br>ADD<br>POP a | <pre># Push b onto stack # Push c onto stack # Add top two items # on stack and replace # with sum # Remove top of stack # and store in a</pre> |

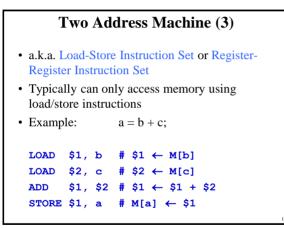

### **Two Address Machine (1)**

- a.k.a. Register-Memory Instruction Set

- One operand may be a value from memory

- Machine has n general purpose registers

\$0 through \$n-1

- Example: a = b + c;

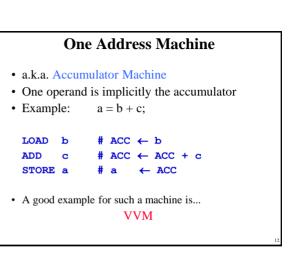

LOAD \$1, b # \$1  $\leftarrow$  M[b] ADD \$1, c # \$1  $\leftarrow$  \$1 + M[c] STORE \$1, a # M[a]  $\leftarrow$  \$1

#### **Two Address Machine (2)**

- a.k.a. Memory-Memory Machine

- Another possibility do stuff in memory!

- These machines have registers used to compute memory addresses

- 2 addresses (One address doubles as operand and result)

- Example: a = b + c;

MOVEa, b#  $M[a] \leftarrow M[b]$ ADDa, c#  $M[a] \leftarrow M[a] + M[c]$

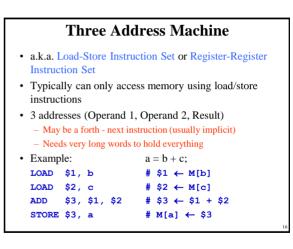

| Number of Addresses | Symbolic Representation | Interpretation   |

|---------------------|-------------------------|------------------|

| 3                   | OP A, B, C              | A ← B OP C       |

| 2                   | OP A, B                 | A ← A OP B       |

| 1                   | OP A                    | AC 🖛 AC OP A     |

| 0                   | OP                      | T ← (T - 1) OP T |

#### **Types of Operand**

- Addresses

- Operand is in the address

- Numbers (actual operand)

- Integer or fixed point

- floating point

- decimal

- · Characters (actual operand)

- ASCII etc.

- Logical Data (actual operand)

- Bits or flags

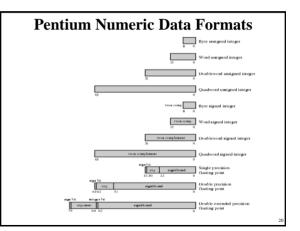

### **Pentium Data Types**

- 8 bit (byte), 16 bit (word), 32 bit (double word), 64 bit (quad word)

- Addressing in Pentium is by 8 bit units

- A 32 bit double word is read at addresses divisible by 4:

0100 1A 22 F1 77 +0 +1 +2 +3

#### **PowerPC Data Types**

- 8 (byte), 16 (halfword), 32 (word) and 64 (doubleword) length data types

- Fixed point processor recognises:

- Unsigned byte, unsigned halfword, signed halfword, unsigned word, signed word, unsigned doubleword, byte string (<128 bytes)</li>

- Floating point

- IEEE 754

- Single or double precision

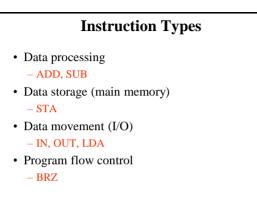

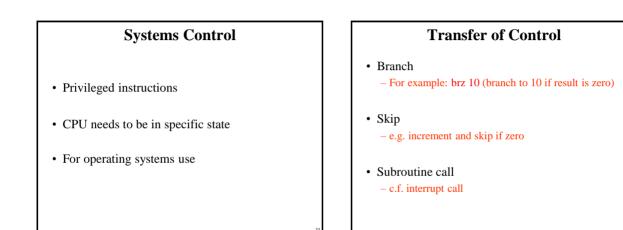

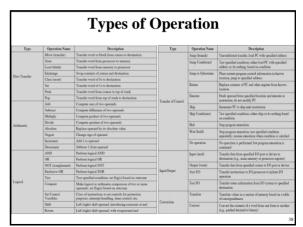

#### **Types of Operation**

- Data Transfer

- Arithmetic

- Logical

- Conversion

- I/O

- System Control

- Transfer of Control

# Data Transfer

- · Need to specify

- Source

- Destination

- Amount of data

- May be different instructions for different movements

- Or one instruction and different addresses

#### Arithmetic

- Basic arithmetic operations are...

- AddSubtract

- Subtract

Multiply

- Divide

- Increment (a++)

- Decrement (a--)

- Negate (-a)

- Absolute

- · Arithmetic operations are provided for...

- Signed Integer

- Floating point?

- Packed decimal numbers?

#### Logical

| • | Bitwise | operations |

|---|---------|------------|

|---|---------|------------|

- AND, OR, NOT

- Example1: bit masking using AND operation

- (R1) = 10100101

- (R2) = 00001111

- = 00000101• (R1) AND (R2)

- Example2: taking ones coplement using XOR operation

= 10100101

- (R1)

- (R2)

- = 11111111 • (R1) XOR (R2) = 01011010

## **Basic Logical Operations**

| Р | Q | NOT P | P AND Q | P OR Q | P XOR Q | P=Q |

|---|---|-------|---------|--------|---------|-----|

| 0 | 0 | 1     | 0       | 0      | 0       | 1   |

| 0 | 1 | 1     | 0       | 1      | 1       | 0   |

| 1 | 0 | 0     | 0       | 1      | 1       | 0   |

| 1 | 1 | 0     | 1       | 1      | 0       | 1   |

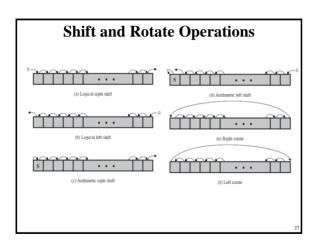

#### **Examples of Shift and Rotate Operations**

| Input    | Operation                       | Result   |

|----------|---------------------------------|----------|

| 10100110 | Logical right shift (3 bits)    | 00010100 |

| 10100110 | Logical left shift (3 bits)     | 00110000 |

| 10100110 | Arithmetic right shift (3 bits) | 11110100 |

| 10100110 | Arithmetic left shift (3 bits)  | 10110000 |

| 10100110 | Right rotate (3 bits)           | 11010100 |

| 10100110 | Left rotate (3 bits)            | 00110101 |

#### An example - sending two characters in a word

- Suppose we wish to transmit characters of data to an I/O device. 1 character at a time.

- If each memory word is 16 bits in length and contains two characters, we must unpack the characters before they can be sent.

- To send the left-hand character:

- Load the word into a register

- AND with the value 1111111100000000

- This masks out the character on the right

#### An example - sending two characters in a word

- Shift to the right eight times

- This shifts the remaining character to the right half of the register

- Perform I/O

- The I/O module reads the lower-order 8 bits from the data bus.

- To send the right-hand character:

- Load the word again into the register

- AND with 000000011111111

- Perform I/O

#### Conversion

- Conversion instructions are those that change the format or operate on the format of data.

- For example:

- Binary to Decimal conversion

# Input/Output

- May be specific instructions - IN, OUT

- May be done using data movement instructions (memory mapped)

- May be done by a separate controller (DMA)

Copyright 2000 N. AYDIN. All rights reserved.

|                     | Transfer data from one location to another                                                                                       |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------|

|                     | If memory is involved:                                                                                                           |

| Data Transfer       | Determine memory address<br>Perform virtual-to-actual-memory address transformation<br>Check cache<br>Initiate memory read/write |

|                     | May involve data transfer, before and/or after                                                                                   |

| Arithmetic          | Perform function in ALU                                                                                                          |

|                     | Set condition codes and flags                                                                                                    |

| Logical             | Same as arithmetic                                                                                                               |

| Conversion          | Similar to arithmetic and logical. May involve special logic to<br>perform conversion                                            |

| Transfer of Control | Update program counter. For subroutine call/return, manage<br>parameter passing and linkage                                      |

| 1/0                 | Issue command to I/O module                                                                                                      |

| 10                  | If memory-mapped I/O, determine memory-mapped address                                                                            |

# Perform Operation Types

| d A registe<br>d pointer i<br>tem Contro |

|------------------------------------------|

|                                          |

|                                          |

|                                          |

|                                          |

|                                          |

| erts a hold<br>instruction               |

| ressor ente<br>roctious ar               |

| ision integ                              |

| it world BU<br>sessor dete               |

| rocessor h                               |

|                                          |

| e global d                               |

| d segment                                |

| ify segmen                               |

|                                          |

| hes the int                              |

| thes the iss                             |

| ilidates a t                             |

|                                          |

|    | indexed by registers ESI and EDI. After each string operation, the registers are                                                                                                                                                                                                  |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | automatically incremented or decremented to point to the next element of the string.                                                                                                                                                                                              |

|    | Load byte, word, dword of string.                                                                                                                                                                                                                                                 |

|    | High-Level Language Support                                                                                                                                                                                                                                                       |

|    | Creates a stack frame that can be used to implement the rules of a block-structured<br>high-level language.                                                                                                                                                                       |

|    | Reverses the action of the previous ENTER.                                                                                                                                                                                                                                        |

|    | Check array bounds. Verifies that the value in operand 1 is within lower and upper<br>limits. The limits are in two adjacent memory locations referenced by operand 2. An<br>intercupt occurs if the value is out of bounds. This instruction is used to check an<br>array index. |

|    | Flag Control                                                                                                                                                                                                                                                                      |

|    | Set Carry flag.                                                                                                                                                                                                                                                                   |

|    | Load A register from flags. Copies SF, ZF, AF, PF, and CF bits into A register.                                                                                                                                                                                                   |

|    | Segment Register                                                                                                                                                                                                                                                                  |

|    | Load pointer into D segment register.                                                                                                                                                                                                                                             |

|    | System Control                                                                                                                                                                                                                                                                    |

|    | Balt.                                                                                                                                                                                                                                                                             |

|    | Asserts a hold on shared memory so that the Pentism has eaclissive use of it during<br>the instruction that immediately follows the LOCK.                                                                                                                                         |

|    | Processor extension except. An escape code that indicates the succeeding<br>instructions are to be executed by a susmeric coprocessor that supports high-<br>precision integer and floating-point calculations.                                                                   |

|    | Whit work BUSY# negated. Suspends Pentisms program execution work the<br>processor detects that the BUSY pin is inserive, indicating that the assumic                                                                                                                             |

|    | coprocessor has finished execution.                                                                                                                                                                                                                                               |

|    | Protection                                                                                                                                                                                                                                                                        |

|    | Store global descriptor table.                                                                                                                                                                                                                                                    |

|    | Load segment limit. Loads a user-specified register with a segment limit.                                                                                                                                                                                                         |

| W. | Verify segment for reading/writing.                                                                                                                                                                                                                                               |

|    | Cache Management                                                                                                                                                                                                                                                                  |

|    | Flushes the internal cache memory.                                                                                                                                                                                                                                                |

|            |                 | 1                                                                                                                                                                  |

|------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Status Bit | Name            | Description                                                                                                                                                        |

| С          | Carry           | Indicates carrying or borrowing into the left-most bit position<br>following an arithmetic operation. Also modified by some of<br>the shift and rotate operations. |

| Р          | Parity          | Parity of the result of an arithmetic or logic operation. 1<br>indicates even parity; 0 indicates odd parity.                                                      |

| А          | Auxiliary Carry | Represents carrying or borrowing between half-bytes of an 8-bit<br>arithmetic or logic operation using the AL register.                                            |

| Z          | Zero            | Indicates that the result of an arithmetic or logic operation is 0.                                                                                                |

| S          | Sign            | Indicates the sign of the result of an arithmetic or logic operation.                                                                                              |

| 0          | Overflow        | Indicates an arithmetic overflow after an addition or subtraction.                                                                                                 |

#### Pentium Conditions for Conditional Jump and SETcc Instructions

| Symbol     | Condition Tested                              | Comment                                                                   |

|------------|-----------------------------------------------|---------------------------------------------------------------------------|

| A, NBE     | C=0 AND Z=0                                   | Above; Not below or equal (greater than,<br>unsigned)                     |

| AE, NB, NC | C=0                                           | Above or equal; Not below (greater than or<br>equal, unsigned); Not carry |

| B, NAE, C  | C=1                                           | Below; Not above or equal (less than,<br>unsigned); Carry set             |

| BE, NA     | C=1 OR Z=1                                    | Below or equal; Not above (less than or equal, unsigned)                  |

| E, Z       | Z=1                                           | Equal; Zero (signed or unsigned)                                          |

| G, NLE     | [(S=1 AND O=1) OR (S=0<br>and O=0)] AND [Z=0] | Greater than; Not less than or equal (signed)                             |

| GE, NL     | (S=1 AND O=1) OR (S=0<br>AND O=0)             | Greater than or equal; Not less than (signed)                             |

| L, NGE     | (S=1 AND O=0) OR (S=0<br>AND O=1)             | Less than; Not greater than or equal (signed)                             |

| LE, NG     | (S=1 AND O=0) OR (S=0<br>AND O=1) OR (Z=1)    | Less than or equal; Not greater than (signed)                             |

| NE, NZ     | Z=0                                           | Not equal; Not zero (signed or unsigned)                                  |

| NO         | O=0                                           | No overflow                                                               |

| NS         | S=0                                           | Not sign (not negative)                                                   |

| NP, PO     | P=0                                           | Not parity; Parity odd                                                    |

| 0          | O=1                                           | Overflow                                                                  |

| Р          | P=1                                           | Parity; Parity even                                                       |

| S          | S=1                                           | Sign (negative)                                                           |

| Ι             | MMX              | Instruction Set                                                                                                                     |

|---------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Category      | Instruction      | Description                                                                                                                         |

|               | PADD [B, W, D]   | Parallel add of packed eight bytes, four 16-bit words, or two 32-bit<br>double-words, with wrappenad                                |

|               | PADDS (B. W)     | Add with saturation.                                                                                                                |

|               | PADDUS [B, W]    | Add unsigned with saturation                                                                                                        |

|               | PSUB [B, W, D]   | Subtract with wrapmound                                                                                                             |

|               | PSUBS (B, W)     | Subtract with saturation                                                                                                            |

| Arithmetic    | PSUBUS (B. WI    | Subtract unsigned with saturation                                                                                                   |

|               | PMULHW           | Parallel multiply of four signed 16-bit words, with high-order 16<br>bits of 32-bit sesult chosen                                   |

|               | PMULLW           | Parallel multiply of four signed 16-bit words, with low-order 16 h<br>of 32-bit result chosen.                                      |

|               | PMADDWD          | Parallel multiply of four signed 16-bit words; add together adjacen<br>pairs of 32-bit results.                                     |

|               | PCMPEQ [B. W. D] | Parallel compare for equality, sesuit is mask of 1s if true or 0s if false                                                          |

| Comparison    | PCMPGT [B, W, D] | Parallel compare for greater than, result is mask of 1s if the or 0s a false.                                                       |

|               | PACKUSWB         | Pack words into bytes with unsigned saturation                                                                                      |

|               | PACKSS [WB, DW]  | Pack words into bytes, or doublewords into words, with signed saturation.                                                           |

| Conversion    | PUNPCKH (BW, WD) | Parallel mpack (interfeaved merge) high-order bytes, words, or                                                                      |

|               | DQI              | doublewoods from MMX register.                                                                                                      |

|               | PUNPCKL (BW, WD. | Parallel mpack (interleaved merge) low-order bytes, words, or                                                                       |

|               | DOI              | doublewords from MMX meister.                                                                                                       |

|               | PAND             | 64-bit bitwise logical AND                                                                                                          |

| Logical       | PNDN             | 64-bit hirwise logical AND NOT                                                                                                      |

| roâncar       | POR              | 64-bit bitwise logical OR                                                                                                           |

|               | PXOR             | 64-bit bitwise logical XOR                                                                                                          |

|               | PSEL [W, D, Q]   | Parallel logical left shaft of packed words, doublewords, or<br>quadword by amount specified in MMX register or immediate<br>value. |

| Shift         | PSRL [W, D, Q]   | Parallel logical right shift of packed words, doublewords, or<br>quadword.                                                          |

|               | PSRA [W. D]      | Parallel authmetic right shift of packed words, doublewords, or<br>enadword.                                                        |

| Dots Transfer | MOV [D.Q]        | Move doubleword or quadword to/from MMX register.                                                                                   |

| State Mot     | EMMS             | Empty MMX state (empty FP register) tag bots).                                                                                      |

| Instruction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | Branch-Oriented                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ь           | Unconditional branch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ы           | Branch to target address and place effective address of instruction following the branch<br>into the Link Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| be          | Branch conditional on Count Register and/or on bit in Condition Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 50          | System call to invoke an operating system service                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| trap        | Compare two operands and invoke system trap handler if specified conditions are met.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             | Load/Store                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| lwzu        | Load word and zero extend to left; update source register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ld          | Load doubleword.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| haw         | Load multiple word, load consecutive words into contiguous registers from the target<br>register through general-purpose register 31.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| lswx        | Load a string of bytes into registers beginning with target register; 4 bytes per register;<br>wrap around from register 31 to register 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|             | Integer Arithmetic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| add         | Add contents of two registers and place in third register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| subé        | Subtract contents of two registers and place in third register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| mellw       | Multiply low-order 32-bit contents of two registers and place 64-bit product in third register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| divd        | Divide 64-bit contents of two registers and place in quotient in third register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             | Logical and Shift                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|             | Common terms around a set of the set of the back of the leader of the set of |

AND: two bits of the Condition Register are ANDe

| <b>PowerPC Operation Types</b> |                                                                                                                   |  |  |  |  |  |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                |                                                                                                                   |  |  |  |  |  |

|                                | Floating-Point                                                                                                    |  |  |  |  |  |

| lfs                            | Load 32-bit floating-point number from memory, convert to 64-bit format, and<br>store in floating-point register. |  |  |  |  |  |

| fadd                           | Add contents of two registers and place in third register.                                                        |  |  |  |  |  |

| fmadd                          | Multiply contents of two registers, add the contents of a third, and place result in<br>fourth register.          |  |  |  |  |  |

| fempu                          | Compare two floating-point operands and set condition bits.                                                       |  |  |  |  |  |

|                                | Cache Management                                                                                                  |  |  |  |  |  |

| dcbf                           | Data cache block flush; perform lookup in cache on specified target address and<br>perform flushing operation.    |  |  |  |  |  |

|                                | Instruction cache block invalidate                                                                                |  |  |  |  |  |

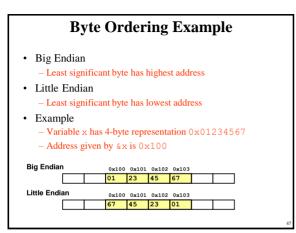

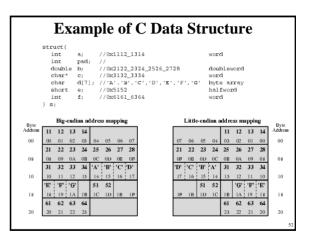

#### **Byte Ordering**

- How should bytes within multi-byte word be ordered in memory?

- Some conventions

- Sun's, Mac's are "Big Endian" machinesLeast significant byte has highest address

- Alphas, PC's are "Little Endian" machines

Least significant byte has lowest address

#### 8

| <b>Representing Strings</b>                                                                                                                                                                                                                                                                               |                                                                                                                                                  |                                            |                                            |         |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------------|---------|--|--|

| Strings in C<br>- Represented by ar<br>- Each character end<br>· Standard 7-bit end<br>· Character "0" has<br>- Digit <i>i</i> has codd<br>- String should be n<br>· Final character =-<br>Compatibility<br>- Byte ordering is n<br>· Data are single by<br>- Text files generall<br>· Except for differe | ray of chara<br>roded in AS<br>oding of char<br>code 0x30<br>0x30+ <i>i</i><br>ull-terminat<br>)<br>ot an issue<br>te quantities<br>y platform i | SCII forn<br>racter set<br>ted<br>independ | Linux/<br>31<br>35<br>32<br>31<br>33<br>00 | Alpha s |  |  |

#### Common file formats and their endian order

- Adobe Photoshop -- Big Endian

- BMP (Windows and OS/2 Bitmaps) -- Little Endian .

- DXF (AutoCad) -- Variable • GIF -- Little Endian

- . IMG (GEM Raster) -- Big Endian

- JPEG -- Big Endian

- . FLI (Autodesk Animator) -- Little Endian

- MacPaint -- Big Endian PCX (PC Paintbrush) -- Little Endian

- PostScript -- Not Applicable (text!) POV (Persistence of Vision ray-tracer) -- Not Applicable (text!)

- QTM (Quicktime Movies) -- Little Endian (on a Mac!) Microsoft RIFF (.WAV & .AVI) -- Both

- . Microsoft RTF (Rich Text Format) -- Little Endian

- SGI (Silicon Graphics) -- Big Endian

- Sun Raster -- Big Endian

- TGA (Targa) -- Little Endian . TIFF

- Both, Endian identifier encoded into file WPG (WordPerfect Graphics Metafile) -- Big Endian (on a PC!)

- **XWD (X Window Dump)** -- Both, Endian identifier encoded into file

Copyright 2000 N. AYDIN. All rights reserved.